介紹

在高(gāo)約束芯片上(shàng)與亞微米波導上(shàng)耦合光的兩種主要方法是光栅或錐形耦合器(qì)。[1]

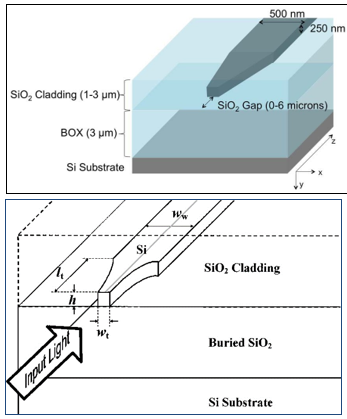

耦合器(qì)由高(gāo)折射率比材料組成,是基于具有(yǒu)納米尺寸尖端的短(duǎn)錐形。[2]

錐形耦合器(qì)實際上(shàng)是光纖和(hé)亞微米波導之間(jiān)的緊湊模式轉換器(qì)。[2]

錐形耦合器(qì)可(kě)以是線性[1]或抛物線性[2]過渡。

選擇Silicon-on-insulator(SOI)技(jì)術(shù)作(zuò)為(wèi)納米錐和(hé)波導的平台,因為(wèi)它提供高(gāo)折射率比,包括二氧化矽層作(zuò)為(wèi)光學緩沖器(qì),并允許與集成電(diàn)子電(diàn)路兼容。[2]

[1] Jaime Cardenas, et al., “High Coupling Efficiency Etched Facet Tapers in Silicon Waveguides,” IEEE Phot. Tech. Lett. VOL. 26, NO. 23, 2380-2382 (2014)

[2] Vilson R. Almeida, et al., "Nanotaper for compact mode conversion," Opt. Lett. 28, 1302-1304 (2003);

3D FDTD仿真

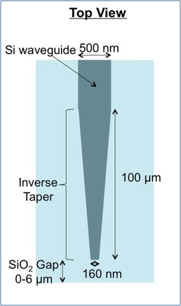

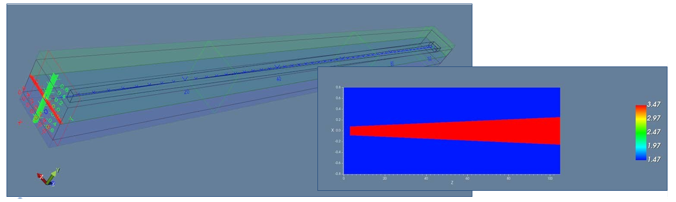

要模拟的關鍵部件是來(lái)自參考文獻[1]的線性錐形矽波導(160 nm至500 nm寬度變化超過100 um長度,250 nm高(gāo)度),它埋在二氧化矽波導中(注意:使用的尺寸減小(xiǎo)了(1.5 umx1.5 umx105 um),以便達到更快的模拟時(shí)間(jiān))

為(wèi)了精确模拟線性錐形矽波導,錐形的網格尺寸應該要設置密度大(dà)一些(xiē),因此在這種情況下使用不均勻的網格。

光源在時(shí)域中設置為(wèi)CW( = 1.55 um),在空(kōng)間(jiān)域上(shàng)設置為(wèi)高(gāo)斯橫向分布,并且位于二氧化矽波導的矽紙尖端。

注意:模拟時(shí)間(jiān)應足夠長,以确保穩态結果

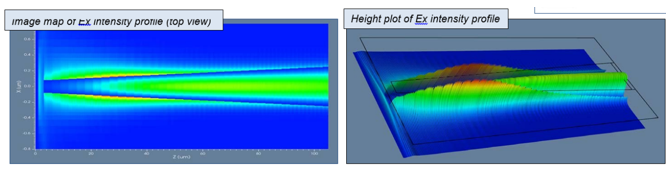

仿真結果

頂視(shì)圖展示了錐形矽波導的有(yǒu)效耦合。

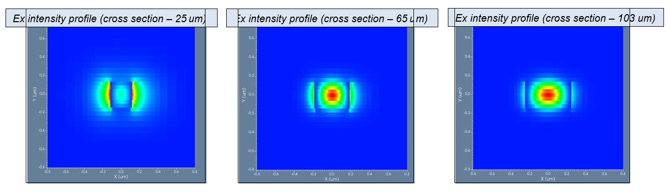

底部視(shì)圖顯示了不同位置的模式轉換(左:25 um,中間(jiān):65 um,右:103 um)

|